电路设计遵循可测试性设计规程(下)

发表时间:2021-03-26 10:23:05 人气:3293

4 、良好的可测试性的机械接触条件

如果不考虑机械方面的基本规则,即使在电气方面具有非常良好的可测试性的电路,也可能难以测试。许多因素会限制电气的可测试性。如果测试点不够或太小,探针床适配器就难以接触到电路的每个节点。如果测试点位置误差和尺寸误差太大,就会产生测试重复性不好的问题。在使用探针床配器时,应留意一系列有关套牢孔与测试点的大小和定位的建议。

5 、最佳可测试性的电气前提条件

电气前提条件对良好的可测试性,和机械接触条件一样重要,两者缺一不可。一个门电路不能进行测试,原因可能是无法通过测试点接触到激活输入端,也可能是激活输入端处在封装壳内,外部无法接触,在原则上这两情况同样都是不好的,都使测试无法进行。在设计电路时应该注意,凡是要用在线测试法检测的组件,都应该具备某种机理,使各个组件能够在电气上绝缘起来。这种机理可以借助于禁止输入端来实现,它可以将组件的输出端控制在静态的高欧姆状态。

虽然几乎所有的测试系统都能够逆驱动( Backdriving )方式将某一节点的状态带到任意状态,但是所涉及的节点最好还是要备有禁止输入端,首先将此节点带到高欧姆状态,然后再“平缓地”加上相应的电平。

同样,节拍发生器总是通过激活引线,门电路或插接电桥从振荡器后面直接断开。激活输入端决不可直接与电路相连,而是通过 100 欧姆的电阻与电路连接。每个组件应有自己的激活,复位或控制引线脚。必须避免许多组件的激活输入端共享一个电阻与电路相连。这条规则对于 ASIC 组件也适用,这些组件也应有一个引线脚,通过它,可将输出端带到高欧姆状态。如果组件在接通工作电压时可实行复位,这对于由测试器来引发复位也是非常有帮助的。在这种情况下,组件在测试前就可以简单地置于规定的状态。

不用的组件引线脚同样也应该是可接触的,因为在这些地方未发现的短路也可能造成组件故障。此外,不用的门电路往往在以后会被利用于设计改进,它们可能会改接到电路中来。所以同样重要的是,它们从一开始就应经过测试,以保证其工件可靠。

6 、改进可测试性

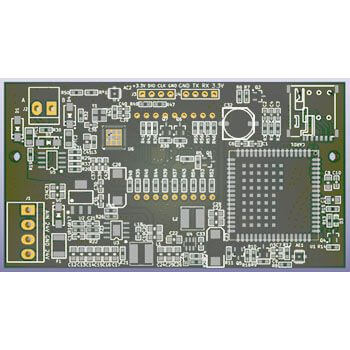

使用探针床适配器时,改进可测试性的建议

套牢孔 呈对角线配置

定位精度为± 0.05mm (± 2mil )

直径精度为± 0.076/-0mm ( +3/-0mil )

相对于测试点的定位精度为± 0.05mm (± 2mil )

离开组件边缘距离至少为 3mm

不可穿通接触

测试点

尽可能为正方形

测试点直径至少为 0.88mm ( 35mil )

测试点大小精度为± 0.076mm (± 3mil )

测试点之间间隔精度为± 0.076mm (± 3mil )

测试点间隔尽可能为 2.5mm

镀锡,端面可直接焊接

距离组件边缘至少为 3mm

所有测试点应可能处于插件板的背面

测试点应均匀布在插件板上

每个节点至少有一个测试点( 100 %信道)

备用或不用的门电路都有测试点

供电电源的多外测试点分布在不同位置

组件标志

标志文字同一方向

型号、版本、系列号及条形码明确标识

组件名称要清晰可见,且尽可能直接标在组件近旁

7 、关于快闪存储器和其它可编程组件

快闪存储器的编程时间有时会很长(对于大的存储器或存储器组可达 1 分钟)。因此,此时不容许有其它组件的逆驱动,否则快闪存储器可能会受到损害。为了避免这种情况,必须将所有与地址总线的控制线相连的组件置于高欧姆状态。同样,数据总线也必须能够被置于隔绝状态,以确保快闪存储器为空载,并可进行下步编程。

系统内可编程组件( ISP )有一些要求,如 Altera , XilinX 和 Lattuce 等公司的产品,还有其它一些特殊要求。除了可测试性的机械和电气前提条件应得到保证外,还要保证具有编程和确证数据的可能性。对于 Altera 和 Xilinx 组件,使用了连串矢量格式( Serial Vector Format SVF ),这种格式近期几乎已发展成为工业标准。许多测试系统可以对这类组件编程,并将连串矢量格式( SVF )内的输入数据用于测试信号发生器。通过边界扫描键( Boundary-Scan-Kette JTAG )对这些组件编程,也将连串数据格式编程。在汇集编程数据时,重要的是应考虑到电路中全部的组件链,不应将数据仅仅还原给要编程的组件。

编程时,自动测试信号发生器考虑到整个的组件链,并将其它组件接入旁路模型中。相反, Lattice 公司要求用 JEDEC 格式的数据,并通过通常的输入端和输出端并行编程。编程后,数据还要用于检查组件功能。开发部门提供的数据应尽可能地便于测试系统直接应用,或者通过简单转换便可应用。

8 、对于边界扫描( JTAG )应注意什么

由基于复杂组件组成精细网格的组件,给测试工程师只提供很少的可接触的测试点。此时也仍然可能提高可测试性。对此可使用边界扫描和集成自测试技术来缩短测试完成时间和提高测试效果。

对于开发工程师和测试工程师来说,建立在边界扫描和集成自测试技术基础上的测试战略肯定会增加费用。开发工程师必然要在电路中使用的边界扫描组件( IEEE-1149.1- 标准),并且要设法使相应的具体的测试引线脚可以接触(如测试数据输入 -TDI ,测试数据输出 -TDO ,测试钟频 -TCK 和测试模式选择 -TMS 以及 ggf. 测试复位)。测试工程师给组件制定一个边界扫描模型( BSDL- 边界扫描描述语言)。此时他必须知道,有关组件支持何种边界扫描功能和指令。边界扫描测试可以诊断直至引线级的短路和断路。除此之外,如果开发工程师已作规定,可以通过边界扫描指令“ RunBIST ”来触发组件的自动测试。尤其是当电路中有许多 ASICs 和其它复杂组件时,对于这些组件并不存在惯常的测试模型,通过边界扫描组件,可以大大减少制定测试模型的费用。

时间和成本降低的程度对于每个组件都是不同的。对于一个有 IC 的电路,如果需要 100 %发现,大约需要 40 万个测试矢量,通过使用边界扫描,在同样的故障发现率下,测试矢量的数目可以减少到数百个。因此,在没有测试模型,或接触电路的节点受到限制的条件下,边界扫描方法具有特别的优越性。是否要采用边界扫描,是取决于开发利用和制造过程中增加的成本费用。衽边界扫描必须和要求发现故障的时间,测试时间,进入市场的时间,适配器成本进行权衡,并尽可能节约。在许多情况下,将传统的在线测试方法和边界扫描方法混合盐业的方案是最佳的解决方式。

相关咨询

工厂展示

联系我们

香港蓝月亮精选二四六

联系人:文先生

手机:13183865499

QQ:1977780637

地址:成都市金牛区星辉西路2号附1号(台谊民生大厦)407号